# Analog to Digital Converter for a Phasemeter

Principal Investigator: Pekka Kangaslahti (386); Co-Investigators: Sungheun Song (University of Michigan), Matt Belz (University of Michigan), Michael P. Flynn (University of Michigan)

Program: FY21 SURP

Strategic Focus Area: Coherent Detectors and Arrays, Remote Sensing Instruments

#### **OBJECTIVES**

The objectives of this research are to develop and demonstrate a low power ADC for the JPL ASIC-based phasemeter. The target ADC specification is a bandwidth of more than 50MHz, digitized with an effective resolution of greater than 10bits. The collaboration will support JPL PEMC strategic investment in task "Mixed-Signal ASIC" to develop ASIC capability at JPL. The phasemeter ASIC development aims at technology development for a nanometer accuracy precision laser instrument.

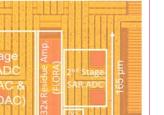

| 1 <sup>st</sup> Stage<br>SAR ADC<br>(Big DAC &<br>Small DAC) | 32x Residue Amp.<br>(FLORA) | 2 <sup>rd</sup> Stage<br>SAR ADC | 165 µm |

|--------------------------------------------------------------|-----------------------------|----------------------------------|--------|

| 276                                                          | um<br>I I I                 |                                  |        |

#### BACKGROUND

□ The performance of the ADC limits the overall performance of the phasemeter.

- □ ASIC implementation promises the most compact and energy-efficient solution This research will research an ADC approach that delivers high performance and is compatible with a ASIC implementation.

- The ASIC approach is difficult as the ADC needs to operate alongside digital circuitry

- SAR-assisted pipeline ADCs have dominated high-performance, high efficiency analog-to digital conversion for more than a decade

- The gain inaccuracy and the power consumption of the residue amplifiers limit pipeline-ADC performance and efficiency

- National Aeronautics and Space Administration

Jet Propulsion Laboratory California Institute of Technology Pasadena, California

www.nasa.gov

Figure 1: Fabricated Chip Micrograph

# **APPROACH**

- □ The first phase of this project will consider the overall system requirements and choose the optimum ADC architecture

- □ The next phase of the project will integrate other analog and digital components of the phase meter with the ADC

- □ A new amplifier is designed to improve the efficiency of the SAR-assisted pipeline ADC

- □ The fully dynamic floating ring amplifier eliminates need for bias and common mode feedback

- □ ADC uses 6b 1st-stage SAR ADC, a 32x residue amplifier, a 9b 2nd-stage SAR ADC

## **BENEFITS TO JPL**

Significant impact on JPL's capabilities is inherent to this project as JPL will gain insight into high performance ADC designs and obtain the IP for use in JPL's CMOS design library being developed in Mixed Signal ASIC PEMC task. These ADCs and the ASIC IP will make possible significant reductions in power, size and mass of future gravity measurements.

PI/Task Mgr Contact Email: Pekka.P.Kangaslahti@jpl.nasa.gov

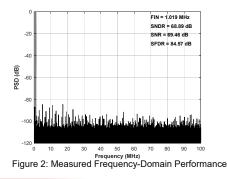

### RESULTS

- A prototype ADC is implemented in a 28 nm CMOS process

- The entire ADC consumes 2.7mW from a 1.1V supply when operating at 200MS/s

- Measured SNDR for a lowfrequency input signal is 68.9dB