FY23 Topic Areas Research and Technology Development (TRTD)

# Direct Energy Transfer Solar Array Architecture with Inherent Array Collapse Prevention

Principal Investigator: Christopher Stell (346); Co-Investigator: Andre Sukernik (346)

Intern Support: Sophia Du, Justin Lee

Strategic Focus Area: Power generation

# BACKGROUND

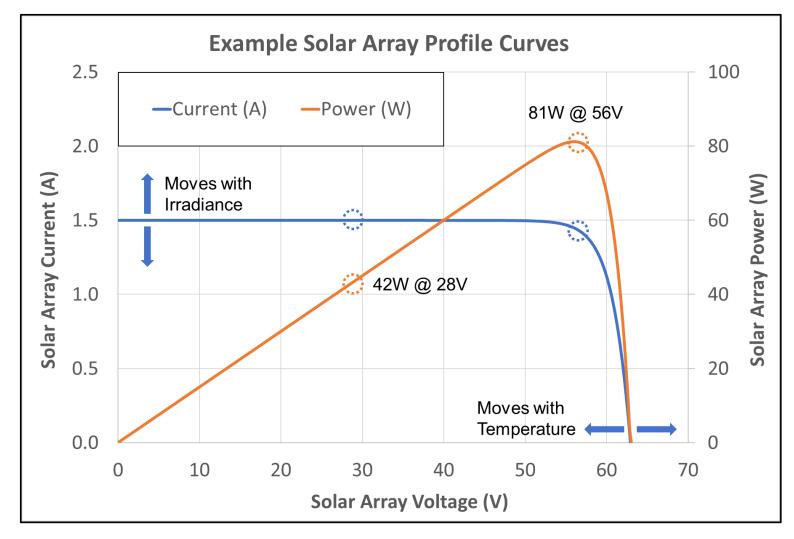

Energy sources like Solar Arrays and RTGs have a characteristic Current – Voltage profile where there is nominally a single maximum power point.

# **CONVENTIONAL SYSTEMS**

#### **String Switchers**

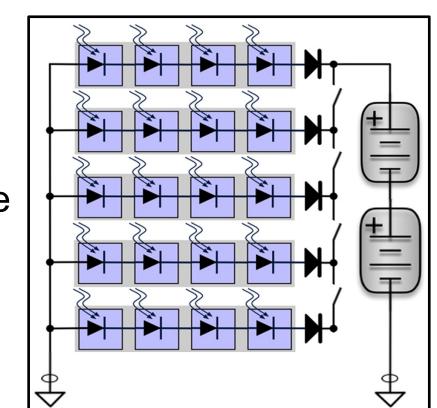

String switchers are simple and Robust, but they operate in Direct Energy Transfer by directly connecting the Solar Array to the Battery, leaving power on the array

### State of the Art

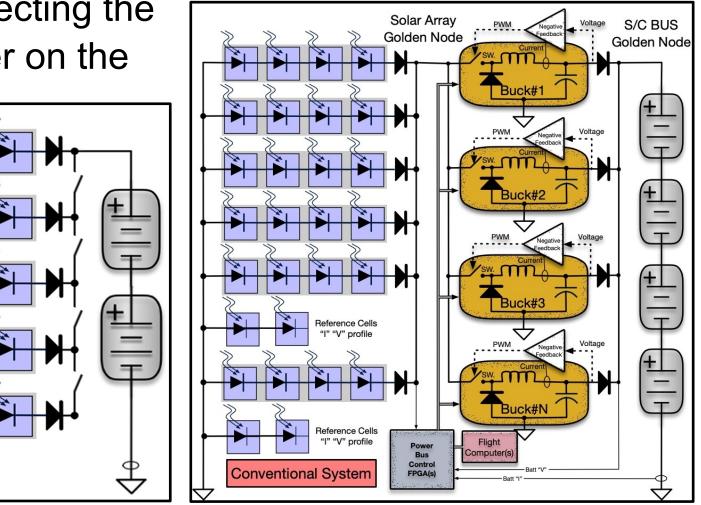

Uses switching converters with negative feedback, and can require large capacitive banks to mitigate stability concerns

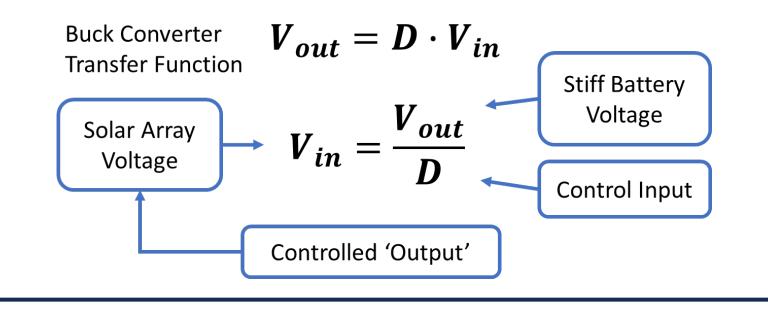

Energy transfer to a battery can be increased by operating at this point. By slowly adjusting the duty cycle (**D**) of a power converter, the voltage of the source is adjusted without compromising the stability of the system

# **PROPOSED SYSTEM**

### **Key Technology Features**

- Ensures stability by transferring energy from a source to a storage element via an effectively open loop switching regulator

- Converges to and operates at the Maximum Power Point of the energy source by using a simple perturb & observe algorithm running on an MCU

- Generates I-V profiles of the energy source without dedicated test cells

- Optimizes noise characteristics by operating with temporally phased switching

- Optimizes conversion efficiency by utilizing GaN switches and smart diode circuits

# HARDWARE DEVELOPMENT

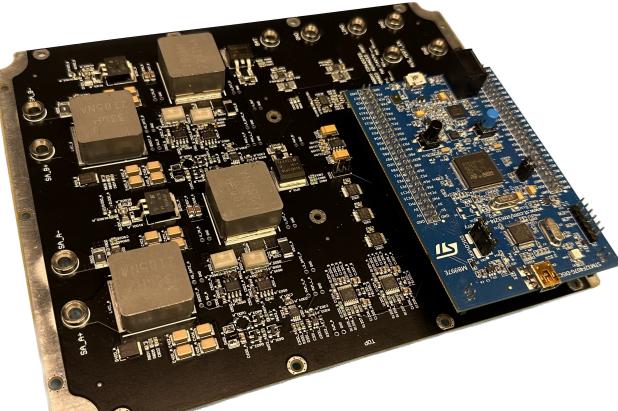

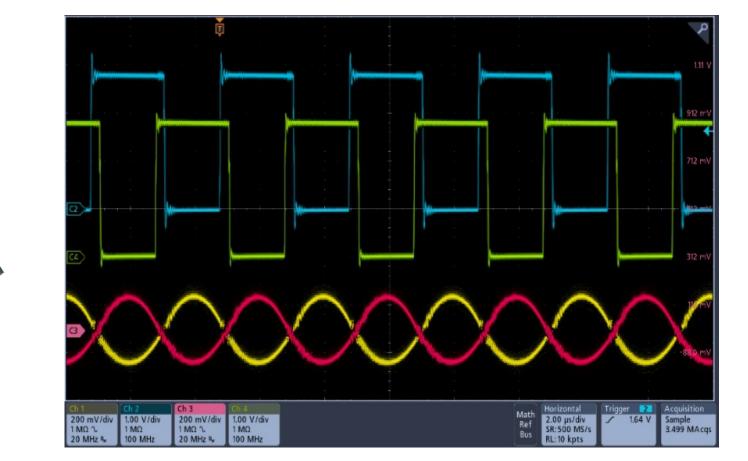

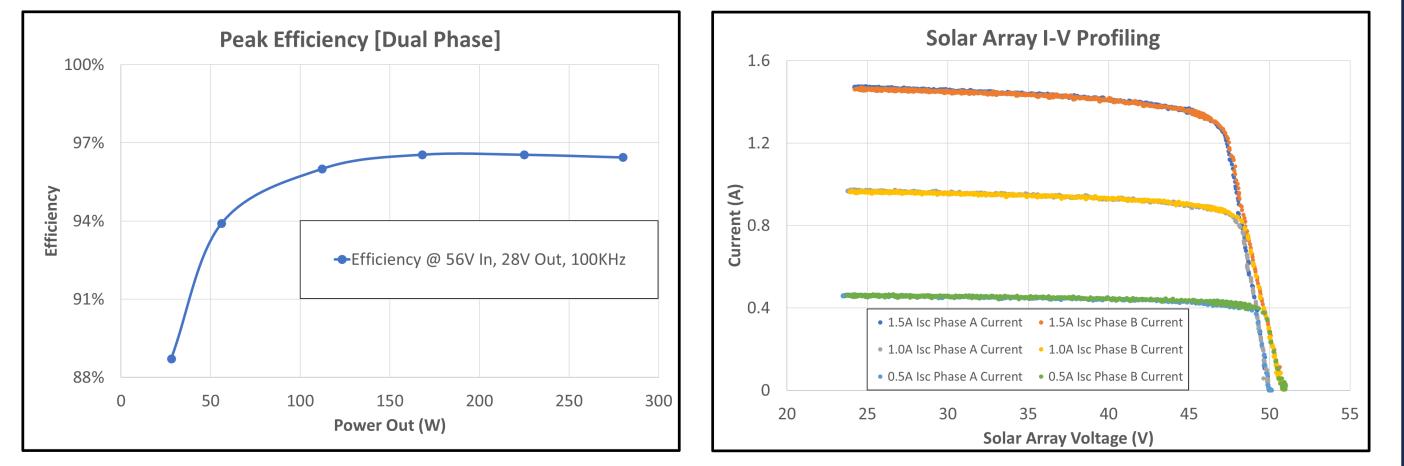

Clockwise from upper left: (1) PWA of a breadboard Bi-Phase Buck Converter implemented with GaN switches, with MCU daughter-card. (2) Oscilloscope view showing the duty cycle control variable and resulting voltage ripple with 180° phase separation. (3) Efficiency plot showing 96.5% peak power conversion efficiency. (4) MCU-generated direct I-V profile of the solar array simulator at 3 different irradiance levels

#### **National Aeronautics and Space Administration**

#### Jet Propulsion Laboratory

California Institute of Technology Pasadena, California www.nasa.gov

#### Clearance Number: CL#00-0000 Poster Number: RPC# Copyright 2023. All rights reserved.

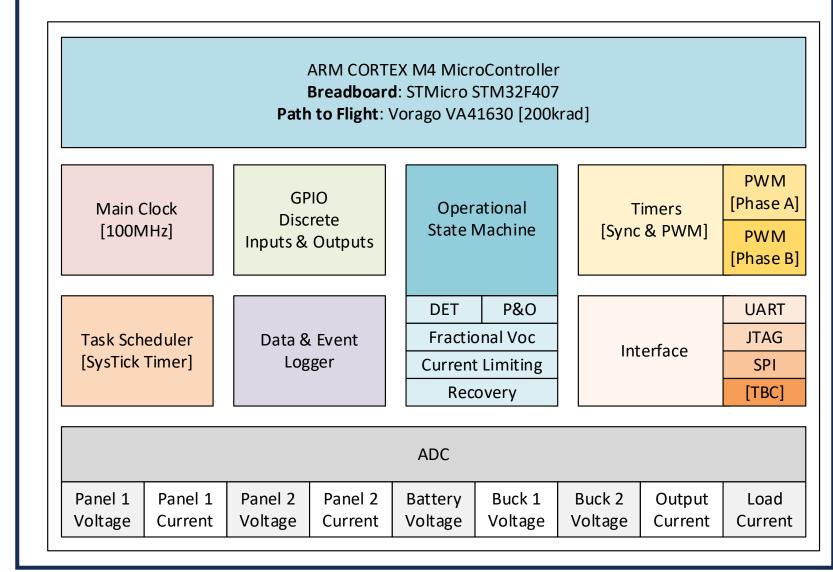

## **MCU DEVELOPMENT**

A Time-Triggered Embedded System, written in C, showed 97-99% convergence to the MPP

| Sponsor | Topical R&TD                     |

|---------|----------------------------------|

| PI      | Chris Stell                      |

| Phone   | 805-990-0486                     |

| Email   | christopher.b.stell@jpl.nasa.gov |